关于 Intel Pentium III Xeon

Pentium III Xeon 于 1999 年 3 月推出。早期版本(代号 Tanner)内置 0.25 微米技术,具有 100MHz 前端总线、512KB 至 2MB 大小的 L2 芯片外高速缓存和最多支持 8 个 CPU 的多处理器。1999 年 10 月,英特尔推出了第二代 PIII Xeon Cascades,使用与 0.18 微米 Pentium III Coppermine 处理器相同的内核。因此,Cascades 具有以全时钟速度运行的 256KB 芯片上 L2 缓存以及所有其他 Coppermine 功能,例如高级传输缓存、高级系统缓冲、支持 133 MHz 前端速度总线、SSE(流 SIMD 扩展)等。

然而,Cascades 的引入有一些严重的缺点:偏小的 256KB 的二级缓存削弱了至强对标准 Pentium III 的性能提升,并且 133MHz 总线协议在一个系统中不支持超过 2 个 CPU。2000 年 5 月,英特尔终于发布了具有高达 2MB(芯片上)二级缓存和 100MHz 前端总线的“大型缓存”版本,再次支持多达 8 个 CPU。

Introduction

The Pentium III Xeon was introduced in March 1999. Early versions (Code named Tanner) where built in .25 micron technology and featured a 100MHz front side bus, 512KB to 2MB L2 off-die cache sizes and multiprocessor support for up to 8 CPUs. In October 1999 Intel introduced the 2nd generation PIII Xeon Cascades, using the same core as the .18 micron Pentium III Coppermine processor. As a result the Cascades has its 256KB on-die L2 cache running at full clock speed and all the other Coppermine features like Advanced Transfer Cache, Advanced System Buffering, support for 133 MHz front speed bus, SSE (Streaming SIMD Extensions), etc.

However, the introduction of Cascades had some severe drawbacks: The small 256KB L2 cache took back the Xeon’s performance advance over the standard Pentium III and the 133MHz bus protocol did not support more than 2 CPUs in a system. In May 2000 Intel finally released a “large cache” version with up to 2MB (on-die) L2 cache and 100MHz front side bus, again supporting multiprocessing with up to 8 CPUs.

我的收藏

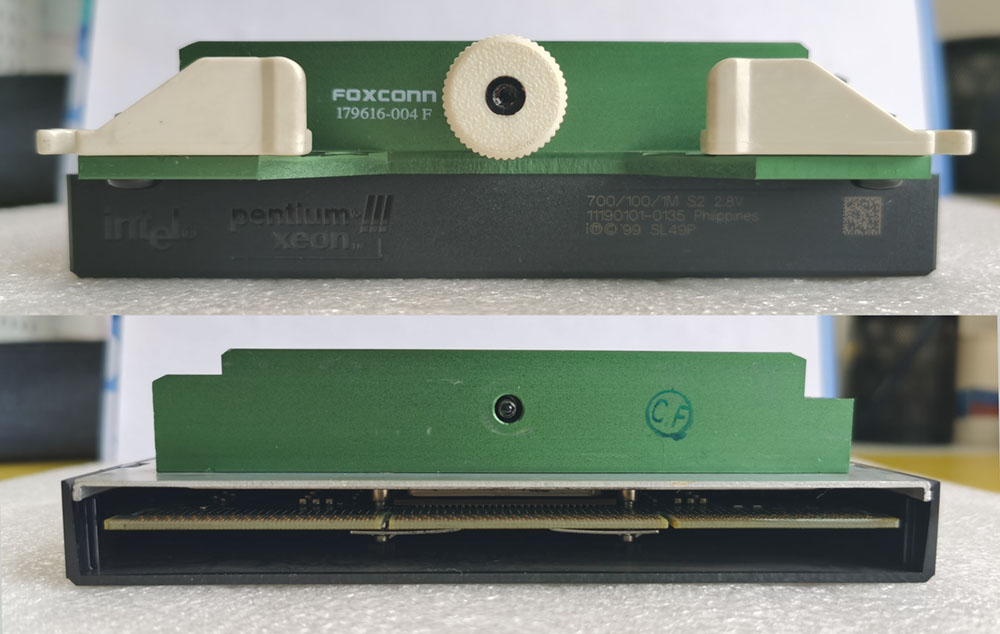

Intel Pentium III Xeon 700/100/1M S2 2.8V

| 参数 | 数值 |

|---|---|

| CPU 类型 | 330-Pin S.E.C.C.PLGA |

| 核心 | Cascades |

| Socket | Slot 2 |

| 主频 | 700 MHz |

| 外频 | 100 MHz |

| 倍频 | x 7 |

| 总线带宽 | 64/32 Bit |

| 一级缓存 | 32 KB (16/16) |

| 二级缓存 | 1024 KB |

| 晶体管 | 28,000,000 |

| 制造工艺 | 0.18 µm |

| 电压 | 2.8 V |

| 步进 | SL49P |

| 生产日期 | 19/2001 |

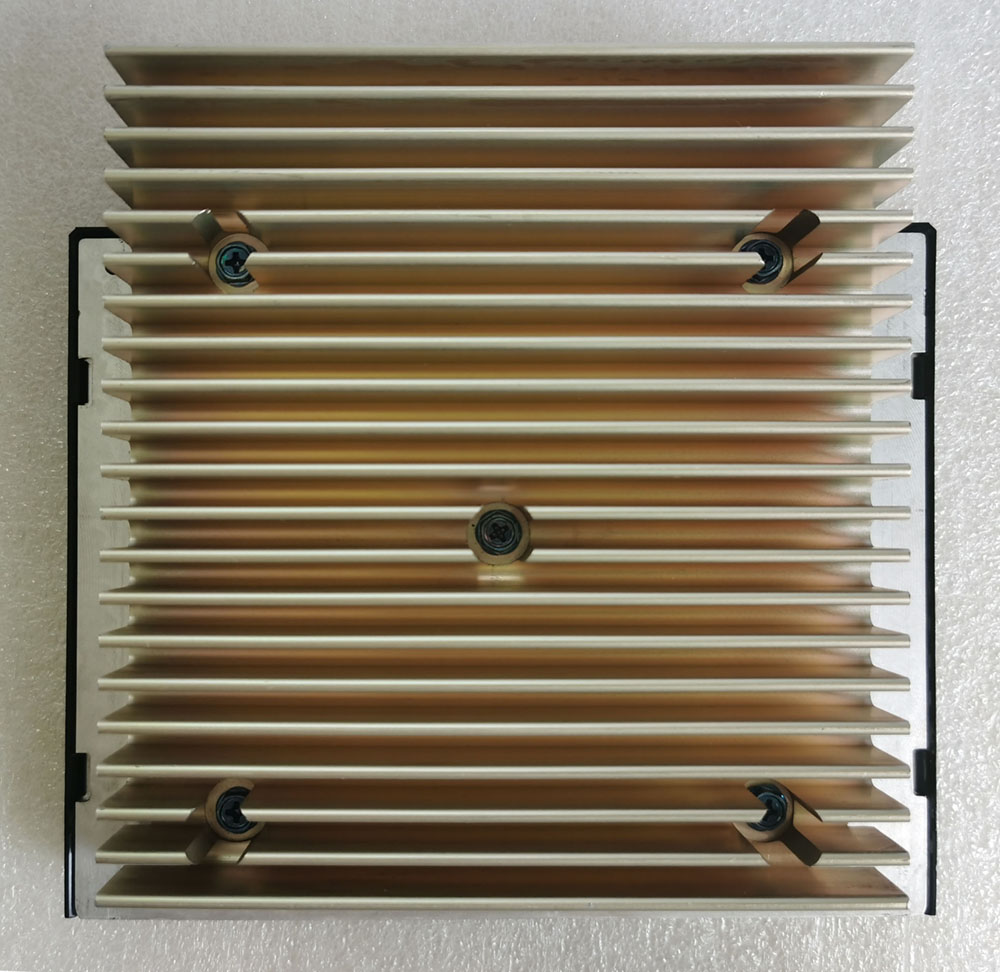

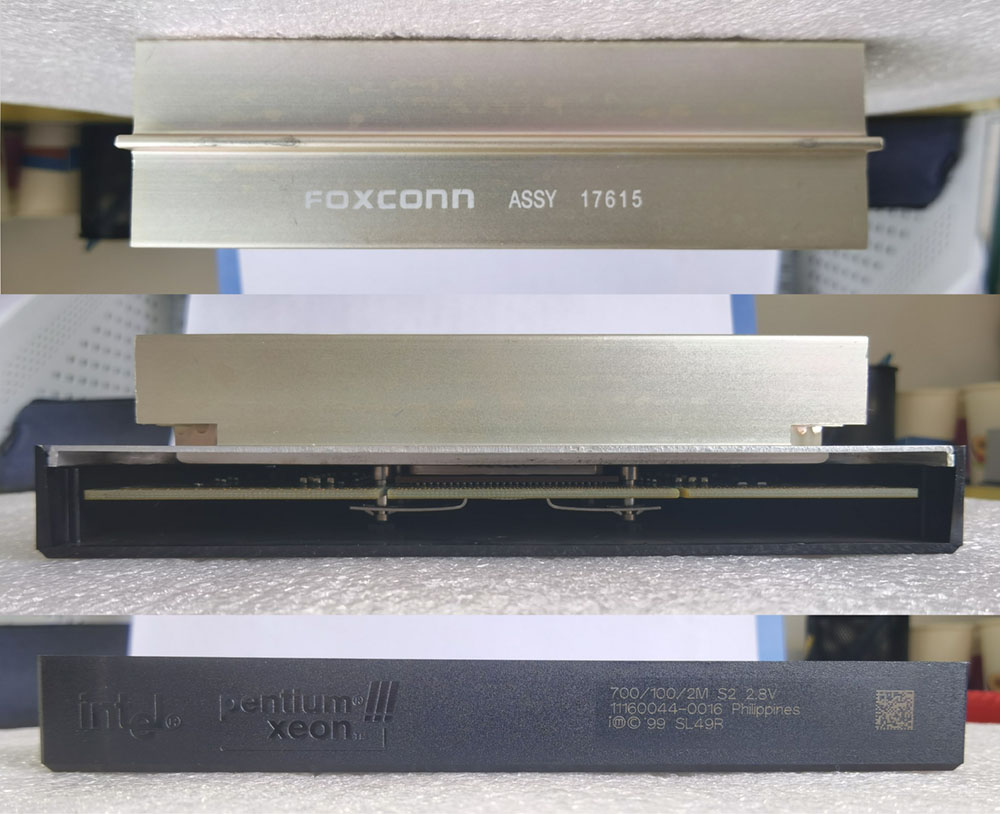

Intel Pentium III Xeon 700/100/2M S2 2.8V

| 参数 | 数值 |

|---|---|

| CPU 类型 | 330-Pin S.E.C.C.PLGA |

| 核心 | Cascades |

| Socket | Slot 2 |

| 主频 | 700 MHz |

| 外频 | 100 MHz |

| 倍频 | x 7 |

| 总线带宽 | 64/32 Bit |

| 一级缓存 | 32 KB (16/16) |

| 二级缓存 | 2048 KB |

| 晶体管 | 28,000,000 |

| 制造工艺 | 0.18 µm |

| 电压 | 2.8 V |

| 步进 | SL49R |

| 生产日期 | 15/2001 |